# 3-bit Implementation Meeting

### Charge:

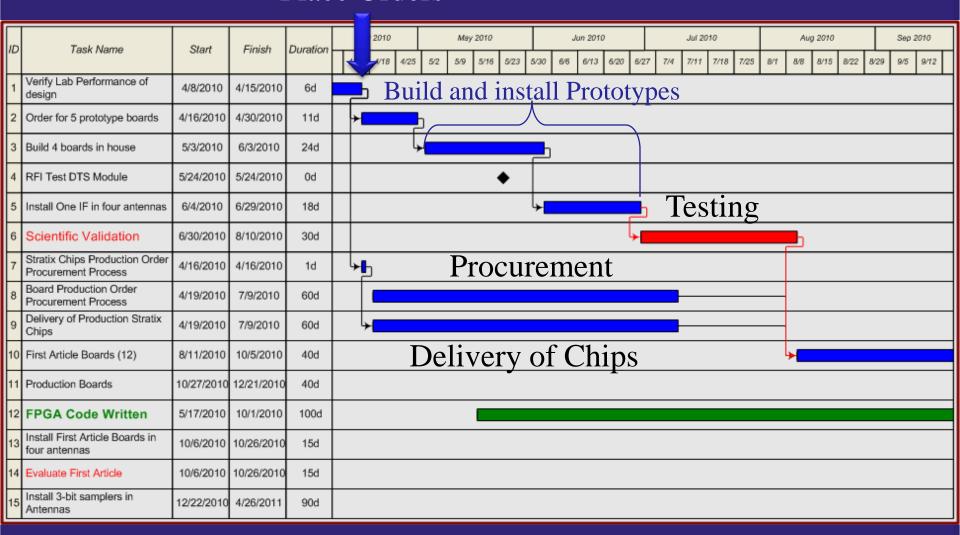

Identify all requirements and implications to install the 3-bit sampler on all antennas by May 2011

#### Place Orders

# EVLA

|    |                                                       |            |            |        | J        | W 2010 | Γ    |           | Aug 2  | 2010 |      | Т    | 5    | Эөр 2010 |         | Т   |          | Oct  | 2010  | 0          |        |      | N     | lov 201 | )     |      |      | E      | Dec 201 | 10       | $\Box$ |       |

|----|-------------------------------------------------------|------------|------------|--------|----------|--------|------|-----------|--------|------|------|------|------|----------|---------|-----|----------|------|-------|------------|--------|------|-------|---------|-------|------|------|--------|---------|----------|--------|-------|

| ΙD | Task Name                                             | Start      | art Finish | Finish | Duration | r      | 7/25 | ļ         | 8/1 8/ | 3 8  | 8/15 | 8/22 | S/29 | 9/5      | 9/12 9/ | /19 | 9/26     | 10/3 | 10/10 | 10         | V17 10 | 0/24 | 10/31 | 11/7    | 11/14 | 11/2 | 1 11 | 1/28 1 | 2/5     | 12/12    | 12/19  | 12/26 |

| 1  | Verify Lab Performance of design                      | 4/8/2010   | 4/15/2010  | 6d     |          |        | _    |           |        |      |      |      |      |          |         |     |          |      |       |            |        |      |       |         |       |      |      |        |         |          |        |       |

| 2  | Order for 5 prototype boards                          | 4/16/2010  | 4/30/2010  | 11d    |          |        |      |           |        |      |      |      |      |          |         |     |          |      |       |            |        |      |       |         |       |      |      |        |         |          |        |       |

| 3  | Build 4 boards in house                               | 5/3/2010   | 6/3/2010   | 24d    |          |        |      |           |        |      |      |      |      |          |         |     |          |      |       |            |        |      |       |         |       |      |      |        |         |          |        |       |

| 4  | RFI Test DTS Module                                   | 5/24/2010  | 5/24/2010  | 0d     |          |        |      |           |        |      |      |      |      |          |         |     |          |      |       |            |        |      |       |         |       |      |      |        |         |          |        |       |

| 5  | Install One IF in four antennas                       | 6/4/2010   | 6/29/2010  | 18d    |          |        |      |           |        |      |      |      |      |          |         |     |          |      |       |            |        |      |       |         |       |      |      |        |         |          |        |       |

| 6  | Scientific Validation                                 | 6/30/2010  | 8/10/2010  | 30d    |          |        |      |           | )      |      |      |      |      |          |         |     |          |      |       |            |        |      |       |         |       |      |      |        |         |          |        |       |

| 7  | Stratix Chips Production Order<br>Procurement Process | 4/16/2010  | 4/16/2010  | 1d     | Г        |        |      |           |        |      |      |      |      |          |         |     |          | I    | 3     | ele        | ea     | .se  | •     |         |       |      |      |        |         |          |        |       |

| 8  | Board Production Order<br>Procurement Process         | 4/19/2010  | 7/9/2010   | 60d    | F        |        |      | $\exists$ |        |      |      |      |      |          |         |     |          |      |       |            |        |      |       |         |       |      |      |        |         |          |        |       |

| 9  | Delivery of Production Stratix<br>Chips               | 4/19/2010  | 7/9/2010   | 60d    | F        |        |      | $\exists$ |        | F    | irs  | t A  | Art  | icle     | es      |     |          |      |       |            |        |      |       |         |       |      |      |        |         |          |        |       |

| 10 | First Article Boards (12)                             | 8/11/2010  | 10/5/2010  | 40d    |          |        |      | þ         |        |      |      |      |      |          |         |     | <u>_</u> |      |       |            | I      | Pro  | od    | uc      | tic   | n    | U    | ni     | its     |          |        |       |

| 11 | Production Boards                                     | 10/27/2010 | 12/21/2010 | 40d    |          |        |      |           | F      | PC   | ЗA   | C    | od   | le       |         |     |          |      |       | <b>م</b> ا |        |      |       |         |       |      |      |        |         | <u>_</u> |        |       |

| 12 | FPGA Code Written                                     | 5/17/2010  | 10/1/2010  | 100d   |          |        |      |           |        |      |      |      |      |          |         |     | Ь        |      |       | Т          |        |      |       |         |       |      |      |        |         |          |        |       |

| 13 | Install First Article Boards in four antennas         | 10/6/2010  | 10/26/2010 | 15d    |          |        |      |           |        |      |      |      |      |          |         |     | <b>►</b> |      |       |            | P      |      |       |         |       |      |      |        |         |          |        |       |

| 14 | Evaluate First Article                                | 10/6/2010  | 10/26/2010 | 15d    |          |        |      |           |        |      |      |      |      |          |         |     |          |      |       |            | P      |      |       |         |       |      |      |        |         |          |        |       |

| 15 | Install 3-bit samplers in<br>Antennas                 | 12/22/2010 | 4/26/2011  | 90d    |          |        |      |           |        |      |      |      |      |          |         |     |          |      |       |            |        |      |       |         |       |      |      |        |         | <b>+</b> |        |       |

### FPGA Code in DTS

### Code cannot be upgraded remotely

Design of the DTS modules requires module to be removed and opened up to reprogram formatter FPGA code

# Therefore the FPGA code must be finished prior to retrofitting of the DTS modules

Not applicable for initial four modules

Dedicated personnel to finish writing code is needed

### Installation

### Two antennas every week

Remove old modules, Install new DTS modules with 3-bit samplers Update L305 module, install cables

### Two teams of three people to install

Supervisor

Fiber/DTS Tech

LO Tech

Dedicated personnel to upgrade modules in lab

## 3-bit DTS Life Cycle

Remove DTS modules from Antenna

Tue

- Remove RFI shell

- ➤ Add/Replace square support rods

- ► Install 3-bit sampler, power supply, and 3-bit M&C circuit boards Wed

- Replace 8-bit sampler heat sink and backplane

- ➤ Install Isolation amplifier and wire power

- Power up sampler, check power, Program Boards and add Serial Thu/Fri Numbers to circuit boards

- Label front cover and put on test bench, burn in

- Analyze results, perform final checks, close up/re-install RFI shell Fri/Mon

- Ready to be installed on Antenna

Tue

Antenna

| IF's             | D302 | IF's  | D304 |

|------------------|------|-------|------|

| $B_0$            | 27   | $D_0$ | 39   |

| $B_\mathtt{1}$   | 29   | $B_2$ | 41   |

| $D_{\mathtt{1}}$ | 31   | $D_2$ | 43   |

|                  |      |       |      |

| IF's             | D301 | IF's  | D303 |

| IF's             | D301 | IF's  | D303 |

21

23

25

$A_0$

$A_1$

$C_0$

$A_2$

33

35

37

| F | V | IA                                |

|---|---|-----------------------------------|

|   | V | $L/\!\!\!\!-\!\!\!\!-\!\!\!\!\!-$ |

| Down Converters |

|-----------------|

| $A_0 A_1 A_2$   |

| $B_0 B_1 B_2$   |

| $C_0C_1C_2$     |

| $D_0 D_1 D_2$   |

|                 |

#### WIDAR

| IF's                        | D301 | IF's           | D303 |

|-----------------------------|------|----------------|------|

| $A_0$                       | 21   | $C_0$          | 33   |

| $A_1$                       | 23   | $A_2$          | 35   |

| $C_{\scriptscriptstyle 1}$  | 25   | C <sub>2</sub> | 37   |

|                             |      |                |      |

| IF's                        | D302 | IF's           | D304 |

| $B_0$                       | 27   | $D_0$          | 39   |

| $B_1$                       | 29   | $B_2$          | 41   |

| $D_{\scriptscriptstyle{1}}$ | 31   | $D_2$          | 43   |

# Requirements

### Manpower

Must use Correlator and Fiber group to assemble and install modules

Need experienced 1 FTE for DTS assembler/installer

Need experienced 0.5 FTE for writing DTS FPGA Code

### Equipment

Stand alone DTS Test rack capable of analyzing 4 modules simultaneously

Need 2 mini-Laptops, transport carrier

# Implications

#### Schedule

May not be able to replace fiber risers as scheduled

Dedicated personnel means they cannot be used for other projects. Experienced personnel means they require minimal training

VLBA Outfitting of DBE should be complete by Dec 2010

Maintenance days should be every Tuesday during installation period. If installation does not occur for any reason, the schedule slips until the next week.

Two dedicated NRAO vehicles for installation on maintenance days

## Summary

#### Commitment

Correlator commissioning may drive 3-bit Schedule

It is possible the schedule can be met with dedicated manpower and assets identified ..however...

#### Risks

Multiple possibilities to delay installation schedule

Impact on new projects is likely